Dalam beberapa kasus, kita perlu mengakses memori non-kontinu yang terdiri dari berbagai lokasi yang tersebar dalam struktur memori kontinu. Salah satu contoh adalah scatter/gather, suatu teknologi yang digunakan dalam processor SIMD (Single Instruction, Multiple Data) untuk mengumpulkan dan menyebar data yang tersebar di dalam memori.

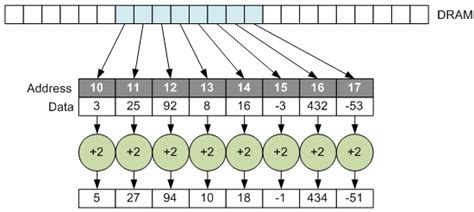

Dalam scatter/gather, SRAM (Static Random Access Memory) berperan sebagai memori terikat ketat (Tightly Coupled Memory), sehingga prosesor dapat memiliki akses cepat ke dalam memori. Sub-banks biru tersebut diisi dari DRAM (Dynamic Random Access Memory) melalui DMA (Direct Memory Access). Karena itu, akan ada dua blok SRAM yang digunakan; satu sedang digunakan sementara lainnya sedang diisi untuk mengurangi dampak waktu yang diperlukan untuk mendapatkan data dari DRAM. Oleh karena itu, seluruh blok yang mengandung tepi seperti yang ditunjukkan di atas mungkin akan dipenuhi ke dalam sub-banks. Jumlah sub-bank yang digunakan ditentukan oleh setiap pelanggan.

Mengakses memori non-kontinu tidaklah mudah, sehingga langkah berikutnya adalah dengan menggunakan blok yang dinamai "Req Q", yang berarti "request queue". Request queue dapat beroperasi secara paralel, sehingga jika Anda memiliki, misalnya, empat lokasi minat, maka Anda dapat memuat empat lokasi tersebut sekaligus. Jika dua lokasi terjadi dalam sub-bank yang sama, maka dua permintaan tersebut akan dipenuhi satu demi lainnya.

Dalam langkah ini, kita tidak secara langsung mendapatkan akses ke data dalam sekali akses. Walaupun kita memberikan kredit untuk DMA yang terjadi di latar belakang dan tidak memerlukan waktu tambahan, mengakses beberapa lokasi dalam sub-bank tunggal harus dilakukan satu demi lainnya. Oleh karena itu, waktu yang diperlukan untuk langkah ini tergantung dari cara data berada di dalam sub-banks.

Saat data diminta, maka logika kontrol akan memasukkan permintaan ke dalam queue dan, ketika data dipenuhi, akan mengarahkan data melalui crossbar (satu siklus jam) ke lokasi register yang sesuai dengan jalan yang memerlukan data tersebut. Permintaan data, sebagai bagian pertama dari dua langkah operasional, mungkin memerlukan waktu yang tidak dapat diprediksi. Hal ini tergantung pada permintaan lainnya yang sedang pending di queue serta sebaran permintaan di dalam sub-banks.

Pada saat register penuh, Anda dapat mengoperasionalkan data dalam operasional single-cycle (atau parallel untuk operasional multi-cycle yang lebih kompleks – semua bagian dari satu-satunya operasi). Inilah saat akses single-cycle menjadi benar.

Berdasarkan biaya pengumpulan data, akan jelas jika Anda ingin melakukan sebanyak mungkin pekerjaan sementara data tersebut berada. Jika Anda memiliki lima tepi yang ingin Anda manipulasi menggunakan tiga operasi, maka kemungkinan lebih cepat untuk melaksanakan semua tiga langkah untuk setiap tepi daripada melakukan semua tepi untuk setiap langkah.

Logika kontrol yang mengontrol seluruh hewan (tidak ditunjukkan pada diagram) tampaknya cukup kompleks. Logika tersebut harus menangkap permintaan yang sedang diproses, mungkin mengambil beberapa permintaan secara tidak sesuai jika mereka terjadi di sub-bank yang kosong. Saya memiliki pertanyaan tentang membaca data ke dalam beberapa bank sementara menulis dari bank lain; itulah saat saya mencapai batas transparansi Cadence. Mereka tidak siap untuk memasuki level detail tersebut.

Dan, berbicara mengenai penulisan kembali, sementara saya telah fokus pada aspek pengumpulan, operasi scatter hampir sama dengan operasi pengumpulan di sebaliknya, kecuali hanya perlu satu instruksi untuk operasi scattering (berbeda dengan operasi pengumpulan dua-fase).

Ada banyak detail lain yang dapat kita eksplorasi, tetapi saya rasa pertanyaan dasar saya telah dijawab: Tidak, Anda tidak mendapatkan akses single-cycle langsung ke lokasi memori non-kontinu DRAM.